Introduction

Circuits logiques: définition, utilisation, technologies utilisées pour la réalisation

- CMOS (Complementary metal-oxyde-semiconductor) est un type de processus de fabrication de transistors à effet de champ métal-oxyde-semiconducteur (MOSFET) qui utilise des paires complémentaires et symétriques de MOSFET de type p et de type n pour les fonctions logiques.

- Le terme CMOS fait référence à la fois à un style particulier de conception de circuits numériques et à la famille de processus utilisés pour mettre en œuvre ces circuits sur des circuits intégrés (puces).

- Les processus et variantes CMOS sont devenus dominants, la grande majorité de la fabrication de circuits intégrés modernes repose sur des processus CMOS.

Technologies anciennes

- Avant les circuits CMOS plusieurs technologies ont dominé le domaine des circuits logiques

Resistor Transistor Logic (RTL)

- Les circuits RTL (Resistor-Transistor Logic) sont une ancienne technologie de conception numérique qui utilise des résistances et des transistors pour réaliser des fonctions logiques. Chaque porte logique est construite à partir de transistors bipolaires et de résistors, permettant l’implémentation de circuits combinatoires et séquentiels. RTL est simple mais limité en termes de vitesse et d’intégration, ce qui a conduit à des technologies ultérieures telles que DTL (Diode-Transistor Logic) et TTL (Transistor-Transistor Logic).

- Ces circuits consommaient beaucoup de puissance car le courant passe constamment dans un des deux états logiques, pour y remédier on pourrait utiliser une grande résistance mais cela limiterait le courant et la tension max de sortie rendant l’état haut difficile à interpreter et agrandirait physiquement la réalisation. C’est pour cela que les circuits RTL ne peuvent pas être aussi petits que les circuits CMOS.

Diode-Transistor Logic (DTL)

- Les circuits DTL (Diode-Transistor Logic) sont une technologie de conception numérique utilisée principalement dans les années 1960 et 1970. Ils combinent des diodes et des transistors pour réaliser des fonctions logiques, offrant une meilleure performance par rapport aux circuits RTL en raison de leur capacité à fonctionner à des vitesses plus élevées. Les diodes dans les circuits DTL permettent de créer des portes logiques qui consomment moins d’énergie lors de la commutation.

Transistor-Transistor Logic (TTL)

- Les circuits TTL (Transistor-Transistor Logic) sont une technologie de conception numérique courante qui utilise des transistors bipolaires pour réaliser des fonctions logiques. Introduits dans les années 1960, ils offrent des vitesses de commutation rapides et une meilleure fiabilité par rapport aux technologies précédentes, comme RTL et DTL. Les circuits TTL sont largement utilisés dans des applications telles que les composants logiques, les compteurs et les systèmes embarqués. TTL se décline en plusieurs variantes, notamment standard, low-power, et high-speed, permettant une flexibilité d’utilisation.

NMOS Logic

-

Les circuits NMOS (N-type Metal-Oxide-Semiconductor) désignent une technologie de conception de circuits intégrés utilisant des transistors NMOS pour réaliser des fonctions logiques. Dans ces circuits, les transistors NMOS sont activés par une tension positive appliquée à la grille, permettant un passage efficace du courant entre la source et le drain. Les circuits NMOS offrent des vitesses rapides et consomment moins d’énergie par rapport aux technologies précédentes. Cependant, ils présentent des niveaux de fuite plus élevés en raison de la nature des transistors.

-

La logique CMOS consomme environ un septième de l’énergie de la logique NMOS, et environ 10 millions de fois moins d’énergie que la logique transistor-transistor bipolaire (TTL).

MOSFETs

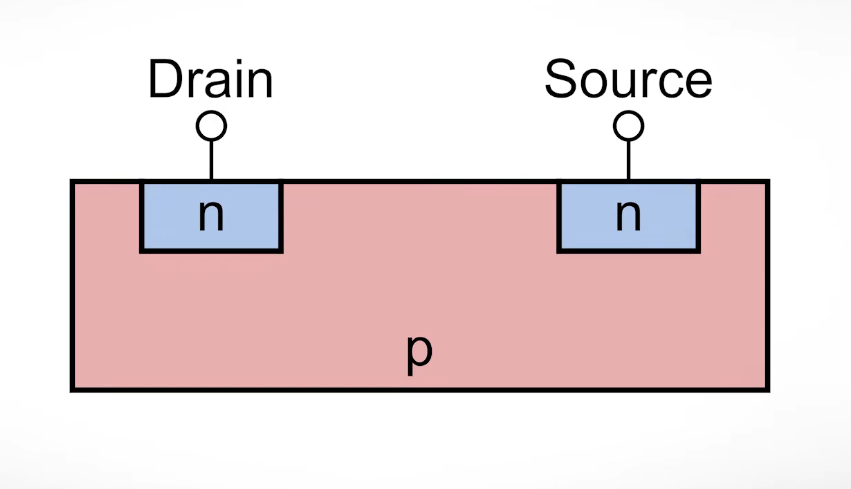

- Les MOSFET (Metal Oxide Semiconductor Field Effect Transistor) sont un type de transistor.

- Le MOSFET se compose de trois régions dopées. Deux puits sont placés dans une masse de matériau semi-conducteur d’un certain dopage (appelé bulk). Deux régions inversement dopées (appelées contacts) sont placés dans ces puits, celles-ci représentent l’Emetteur (Source) et le Collecteur (Drain) du transistor

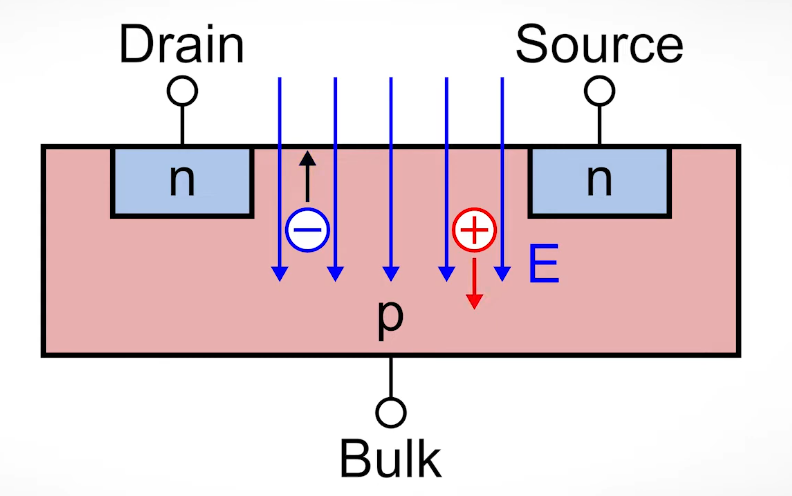

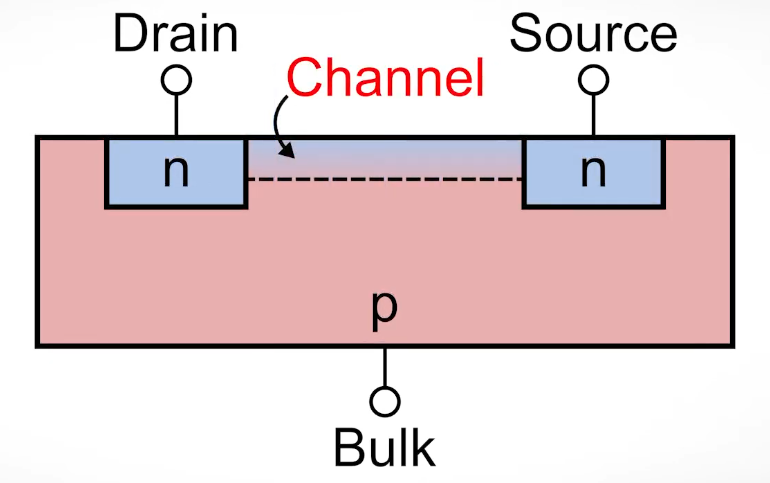

- Le “FE” désigne comment le courant passe à travers le transistor, pour créer un channel entre les deux contacts où le courant peut circuler, on doit fair agir le bulk de la même manière que les contacts ce qui permet au courant de circuler comme si le tout était un seul type de matériau. Ceci est réalisé grâce au Field Effect. Un champ électromagnétique directionnel est appliqué entre les contacts ce qui a pour effet de déplacer les électrons dans la région la chargeant positivement ou négativement selon la direction du champ.

Un channel est donc crée et le courant peut passer.

Un channel est donc crée et le courant peut passer.

- Pour générer le champ électromagnétique, on utilise une électrode placée au dessus du channel. Le “MOS” dans MOSFET vient de la sequence de matériaux positionnés au dessus du channel qui est en ordre:

- Metal pour l’électrode ou le matériau conducteur

- Oxide pour matériau isolant, typiquement le Silicon Dioxyde

- Semiconductor pour le matériau semiconducteur lui même

- Tout ceci forme donc la base (Gate) du transistor ![[IFE - TU Graz - Metal Oxide Semiconductor Field Effect Transistor, MOSFET - Structure, Characteristics, Regions [rNJ7T-Cuc90 - 1412x794 - 4m14s].png]]

- On distingue deux variantes de MOSFETs selon le dopage du bulk et celui de la source et du drain.

- Lorsque le bulk est dopé de type P on dit qu’il s’agit un N-channel MOS ou NMOS

- Lorsque le bulk est dopé de type N on dit qu’il s’agit un P-channel MOS ou PMOS ![[IFE - TU Graz - Metal Oxide Semiconductor Field Effect Transistor, MOSFET - Structure, Characteristics, Regions [rNJ7T-Cuc90 - 1412x794 - 4m23s].png]]

CMOS

Qu’est ce que c’est?

- CMOS ou Complementary Metal Oxide Semi-conductor est technologie utilisé dans la production de circuits logiques à base de semi-conducteurs adoptée universellement depuis les années 80’ et est utilisée jusqu’à ce jour.

Comment ça marche?

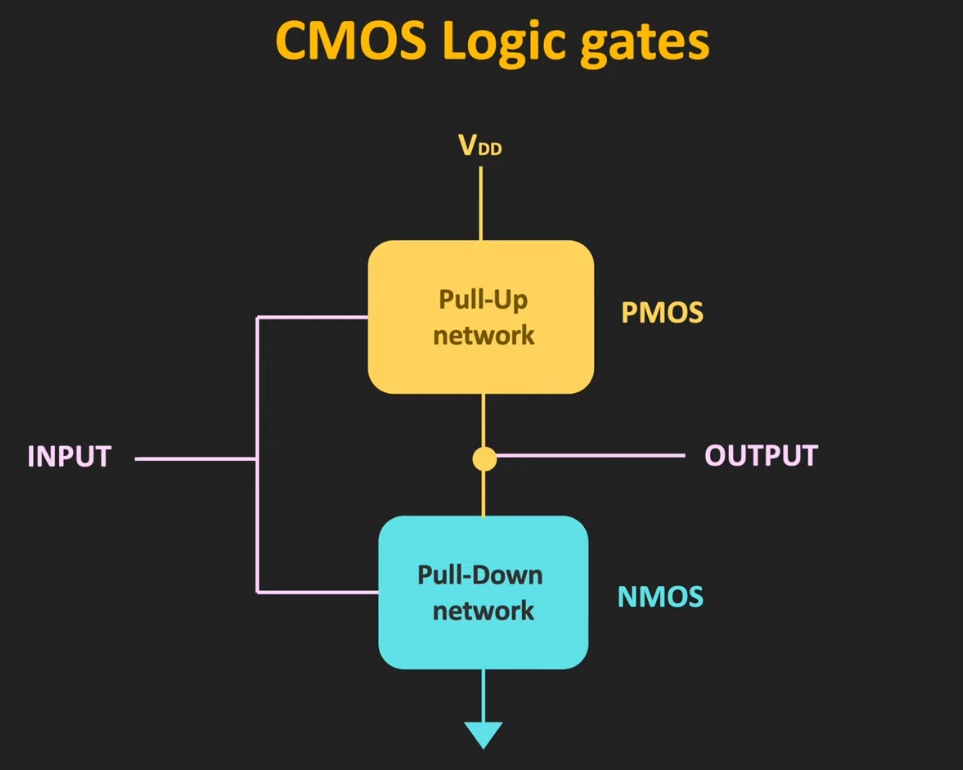

- Les circuits CMOS sont des circuits logiques réalisés à base de paires de transistors MOSFET qui commutent à des niveaux d’entrées opposés, ces transistors sont appelés PMOS et NMOS.

Les circuits CMOS

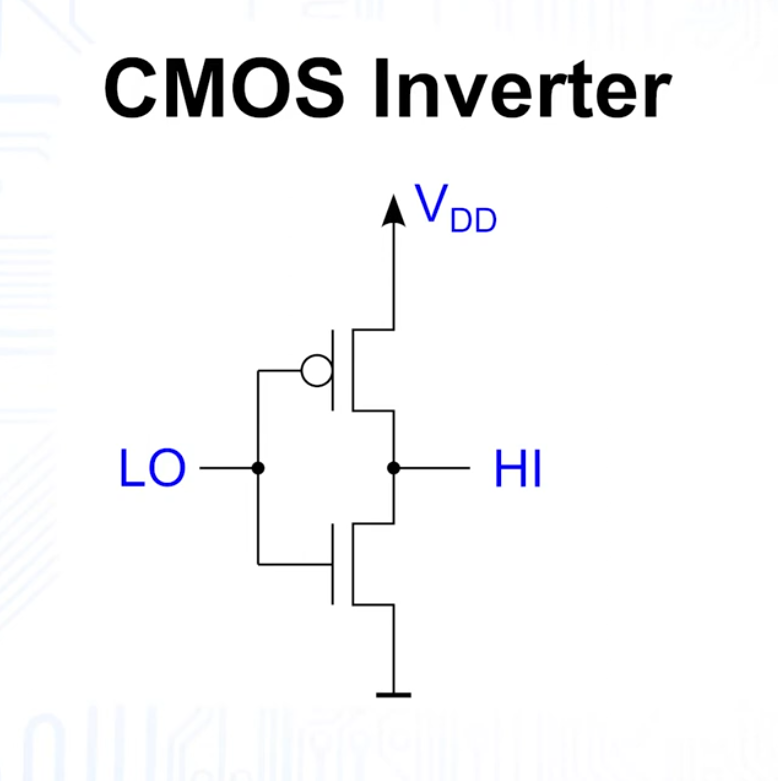

- Les circuits logiques CMOS sont toujours divisés en un réseau pull up composé de PMOS et un réseau pull down complémentaire composé de transistors NMOS.

- Les transistors PMOS sont toujours situés dans la partie pull up du circuit puisque la connexion est directement connectée à la tension d’alimentation, on dit qu’ils transmettent le « 1 » logique fort et le « 0 » logique faible.

- A l’inverse, les transistors NMOS sont toujours dans le réseau pull down puisque leur connexion doit être connectée au potentiel de masse, on dit qu’ils transmettent le « 1 » logique faible et le « 0 » logique fort.

Inverseur

- Inverse le signal d’entrée

Transmission Gate

- Agit comme un disjoncteur et peut être passant ou bloquant dans les deux sens selon un signal de contrôle

- Ce circuit peut être trouvé dans des switches, des multiplexeurs, des mécanismes de sécurité dans des circuits intégrés…etc. ![[IFE - TU Graz - CMOS Basics - Inverter, Transmission Gate, Dynamic and Static Power Dissipation, Latch Up [CwL3ouoN7pE - 1570x883 - 6m09s].png]]

Conception d’un circuit CMOS

- Le moyen le plus simple de concevoir un circuit logique CMOS consiste à dériver d’abord le réseau pull-down à partir de la table de vérité, puis à développer le réseau pull-up complémentaire à partir du réseau pull-down.

- D’abord, il faut obtenir l’équation booléenne du réseau pull-down qui amène la sortie à l’état bas. Il suffit de chercher dans la table de vérité tous les cas où le résultat est à l’état bas.

- Puis on construit le réseau à partir de l’équation on représente la multiplication ou AND logique par des NMOS placés en série et l’addition ou OR logique par des NMOS placés en parallèle. Après avoir construit le réseau, on le relie à la masse.

- Pour dériver le réseau pull-up, il suffit d’inverser les opérations, càd le AND logique sera représenté par des PMOS mis en parallèle et le OR logique sera représenté par des PMOS mis en série. Après avoir construit le réseau, on le relie à l’alimentation.

- La sortie sera obtenue entre la sortie du réseau pull-up et l’entrée du réseau pull-down. Sauf que la particularité des circuits CMOS est que si on utilise des entrées non complémentées, on obtient une sortie complémentée ou inversée, il faudra donc la faire passer par un inverseur pour obtenir la sortie désirée.

Portes Logiques

NAND / AND

NOR / OR

XNOR

Circuits Complexes

- En utilisant la technique abordée précédemment et les circuits des portes logiques élémentaires on peut construire n’importe quel circuit complexe comme les additionneurs, multiplexeurs, décodeurs…etc

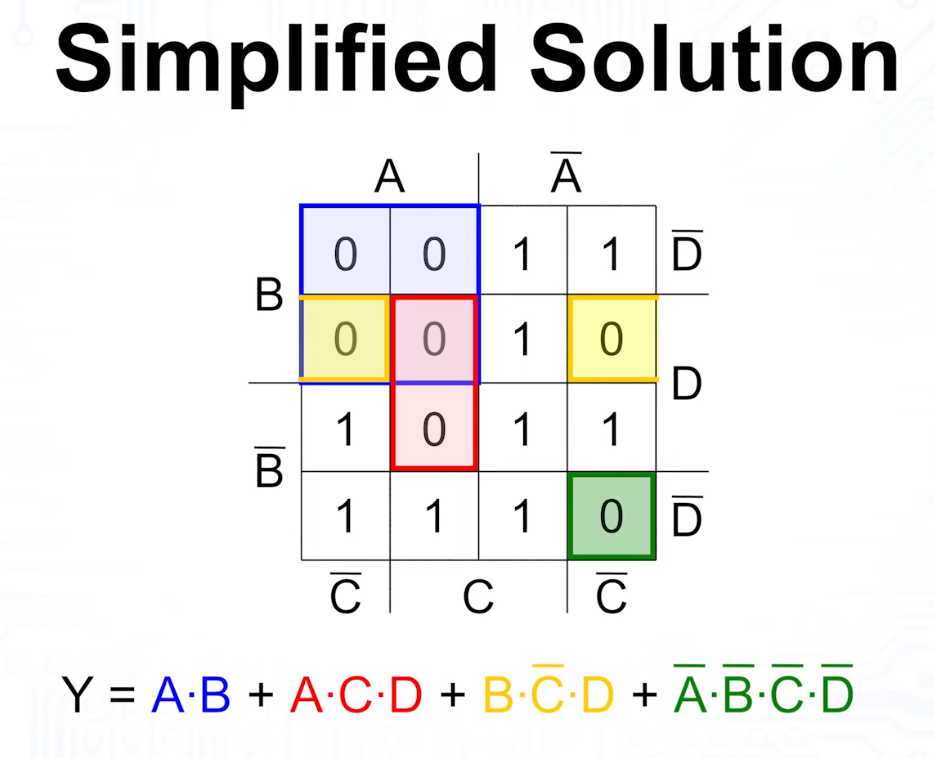

- Lorsqu’on a des circuits complexe à plusieurs entrées on peut utiliser la table de Karnaugh et les propriétés de l’algebre booléenne pour simplifier l’equation booléenne du circuit.

![[IFE - TU Graz - CMOS Circuits - Pull Down and Pull Up Network, PDN, PUN, Karnaugh Map, Digital Logic, NOT, NAND, XOR [xhxQlJ9IlG0 - 1570x883 - 7m53s].png]]

![[IFE - TU Graz - CMOS Circuits - Pull Down and Pull Up Network, PDN, PUN, Karnaugh Map, Digital Logic, NOT, NAND, XOR [xhxQlJ9IlG0 - 1570x883 - 10m34s].png]]

![[IFE - TU Graz - CMOS Circuits - Pull Down and Pull Up Network, PDN, PUN, Karnaugh Map, Digital Logic, NOT, NAND, XOR [xhxQlJ9IlG0 - 1570x883 - 10m34s].png]]

Comment sont-ils produits

Lithographie

Où sont-ils utilisés

µProcesseurs & µContrôleurs

Avantages

Résistance aux bruits

- Les circuits CMOS résistent bien aux bruits grâce à leur architecture différentielle, qui rejette les variations communes. Leur faible consommation d’énergie lorsqu’ils ne commutent pas réduit le bruit thermique généré. De plus, leur impédance élevée rend les entrées moins sensibles aux bruits de faible amplitude. L’isolation des composants et l’intégration de techniques de filtrage améliorent également la qualité du signal en atténuant les interférences.

Power Consumption

Dynamic Power Dissipation

- lors du fonctionnement du circuit, il y a un très court instant pendant lequel les deux transistors commutent simultanément en raison de la capacité de charge, conduisant à une dissipation de puissance de la source d’alimentation directement vers la masse. ![[IFE - TU Graz - CMOS Basics - Inverter, Transmission Gate, Dynamic and Static Power Dissipation, Latch Up [CwL3ouoN7pE - 1570x883 - 5m04s].png]]

Static Power Dissipation

- Courant de fuite - Les MOSFET ne peuvent jamais être entièrement éteints : dans les circuits intégrés modernes, la tension d’alimentation est maintenue aussi basse que possible (ex : les microprocesseurs utilisent 1,1~1,3 V) ![[IFE - TU Graz - CMOS Basics - Inverter, Transmission Gate, Dynamic and Static Power Dissipation, Latch Up [CwL3ouoN7pE - 1570x883 - 5m45s].png]]

Limitations

- Les circuits CMOS consomment beaucoup de puissance lorsqu’ils commutent

- Les pertes dites “dynamiques” sont causées dépanadent linéairement de la fréquence de commutation et la capacité de la charge, et quadratiquement de la tension d’alimentation ![[IFE - TU Graz - CMOS Basics - Inverter, Transmission Gate, Dynamic and Static Power Dissipation, Latch Up [CwL3ouoN7pE - 1570x883 - 9m21s].png]]

- Les pertes dites “statiques” dépanadent linéairement du “leakage current” et de la tension d’alimentation. ![[IFE - TU Graz - CMOS Basics - Inverter, Transmission Gate, Dynamic and Static Power Dissipation, Latch Up [CwL3ouoN7pE - 1570x883 - 9m38s].png]]

- Le “leakage current” est lui-même inversement proportionnel au “channel width” c.à.d. plus on réduit la taille du transistor, plus les pertes statiques augmentent. Celles-ci représentent plus de la moitié des pertes totales depuis l’invention de la technologie 50 nm.

- Ces pertes ne peuvent être évitées dans le CMOS et conduiront probablement à long terme à un changement technologique. ![[IFE - TU Graz - CMOS Basics - Inverter, Transmission Gate, Dynamic and Static Power Dissipation, Latch Up [CwL3ouoN7pE - 1436x808 - 9m47s].png]]

Latch-up

- Un deuxième inconvénient concernant les circuits CMOS est leur sensibilité aux surtensions. Surnommé “Latch-up”, ce problème survient à cause d’une décharge électrostatique, d’une surtension ou d’une condition de fonctionnement anormale.

- Ceci provoque une activation non désirée des transistor par effet de rétroaction, souvent à cause de deux transistors NPN et PNP qui interfèrent l’un avec l’autre dans le circuit.

- Une fois enclenché, le latch-up peut créer un chemin de faible résistance entre l’alimentation et la terre causant une surchauffe puis la destruction du circuit. ![[IFE - TU Graz - CMOS Basics - Inverter, Transmission Gate, Dynamic and Static Power Dissipation, Latch Up [CwL3ouoN7pE - 1436x808 - 10m39s].png]] ![[IFE - TU Graz - CMOS Basics - Inverter, Transmission Gate, Dynamic and Static Power Dissipation, Latch Up [CwL3ouoN7pE - 1436x808 - 11m15s].png]]

- Une des stratégies pouvant être mise en place pour prévenir le latch-up est l’ajout de diodes de protection pour limiter les courants parasites. Cependant, ces diodes supplémentaires signifient également une capacité de charge et un courant de fuite supplémentaires, ce qui entraîne une dissipation de puissance plus élevée. ![[IFE - TU Graz - CMOS Basics - Inverter, Transmission Gate, Dynamic and Static Power Dissipation, Latch Up [CwL3ouoN7pE - 1436x808 - 11m44s].png]]

Futur des CMOS

- Plus on vise à miniaturiser les circuits CMOS et donc les transistors (en dessous de 20nm), plus les limitations des transistors MOSFET traditionnels deviennent significatives.

- Heureusement, alors que de nouvelles technologies sont développées et adoptées, les circuits CMOS continuent d’évoluer et de s’améliorer. Les principaux défis que ces nouvelles technologies visent à adresser sont les vitesses de commutation, la consommation d’énergie dynamique et les fuites de courant statique.

- Contrairement aux MOSFETs traditionnels dits “planar”, plats ou 2D, ces nouvelles technologies sont “non-planar”, verticals ou 3D.

Technologies FinFET

- La technologie FinFET se caractérise par sa structure en trois dimensions, où le canal est formé par un “fin” vertical qui émerge du substrat, permettant à la grille d’entourer le canal sur plusieurs côtés. Cette conception améliore le contrôle électrostatique sur le canal, réduisant ainsi les effets de court-circuit qui se manifestent à des dimensions nanométriques.

Technologies GAAFET / MBCFET

-

Dans les GAAFETs (Gate-All-Around Field-Effect Transistor), la grille entoure complètement le canal, non seulement sur les côtés, mais aussi sur le dessus, ce qui permet un contrôle électrostatique encore plus précis. Cette configuration permet de minimiser les effets de court-circuit et d’améliorer la performance des dispositifs à des échelles nanométriques.

-

Le MBCFET (Multi-Bridge Channel FET) se distingue par sa structure de canal en forme de pont, permettant une utilisation de matériaux à haute mobilité électronique. Cette conception favorise un meilleur contrôle électrostatique et réduit les courants de fuite, offrant ainsi une efficacité énergétique accrue.

-

Ces technologies incluent une réduction significative des courants de fuite, une meilleure efficacité énergétique et des vitesses de commutation accrues. Ces caractéristiques les rendent particulièrement adaptés aux applications avancées, y compris les microprocesseurs et les circuits intégrés à haute performance.

- Les FinFETs sont déjà le standard utilisé dans la majorité des applications à haute performance notamment dans les microprocesseurs modernes (16~3nm)

- Les GAAFETs et MBCFETs sont encore en phase développement notamment par Intel et Samsung respectivement.

Sources

Metal Oxide Semiconductor Field Effect Transistor, MOSFET - Structure, Characteristics, Regions CMOS Basics - Inverter, Transmission Gate, Dynamic and Static Power Dissipation, Latch Up CMOS Circuits - Pull Down and Pull Up Network, PDN, PUN, Karnaugh Map, Digital Logic, NOT, NAND, XOR

- Final result